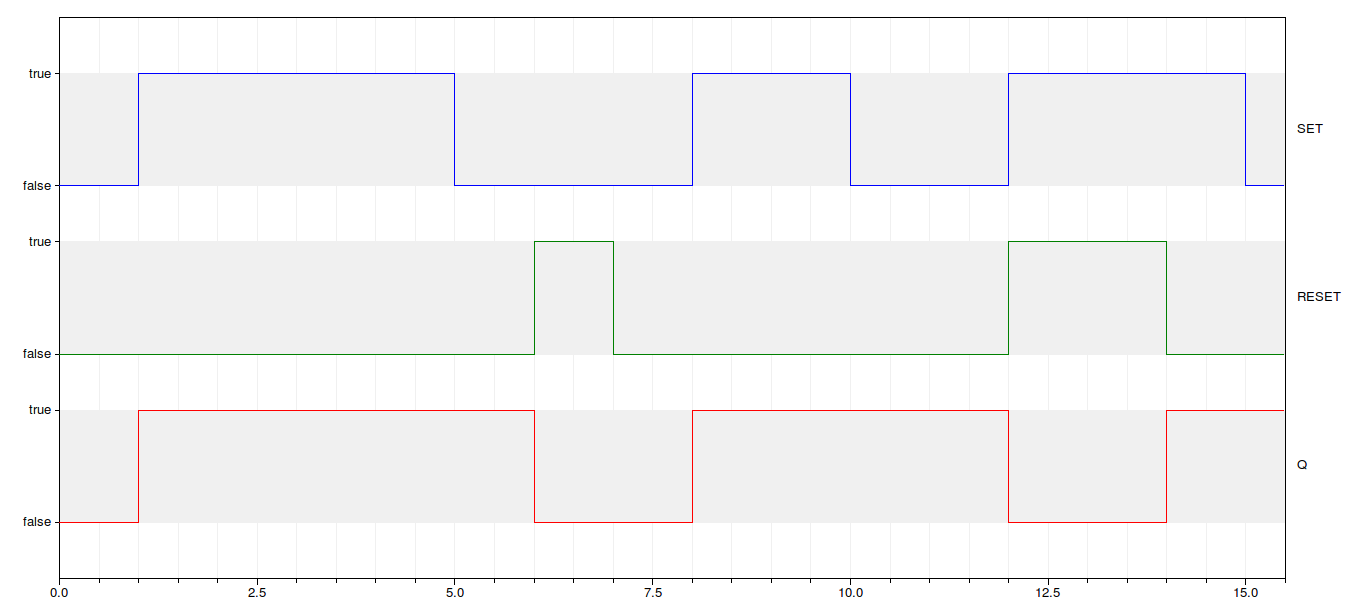

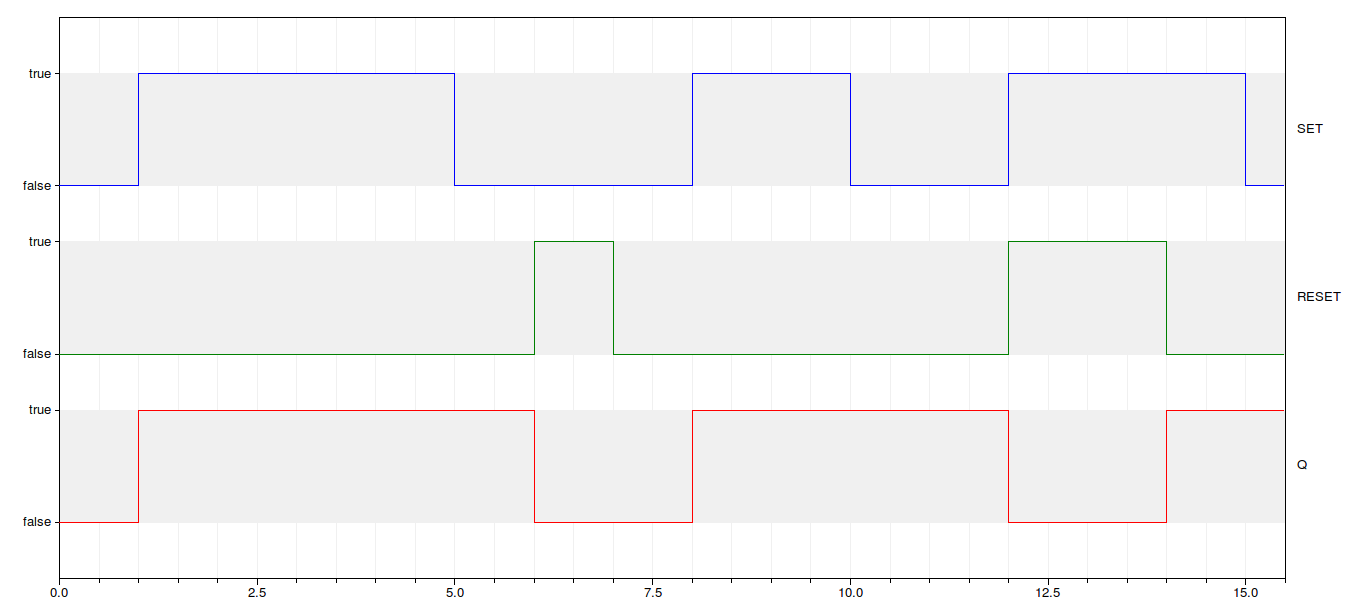

Flip Flop test

Description

In this examples is tested the Set reset Flip Flop.

In this case Ts = 0.1 and the initial

value of the FF is Q = false.

When a rising edge of the SET signal is detected, the output Q

becomes true while a rising edge of the RESET signal is detected

the output Q becomes false.

- First release of the Industrial Control Systems: April-May

2012

-

- List of revisions:

-

- 11 May 2012 (author: Marco Bonvini)

- Main Authors:

- Marco Bonvini; <bonvini@elet.polimi.it>

- Alberto Leva <leva@elet.polimi.it>

- Politecnico di Milano

- Dipartimento di Elettronica e Informazione

- Via Ponzio 34/5

- 20133 Milano - ITALIA -

- Copyright:

- Copyright © 2010-2012, Marco Bonvini and Alberto

Leva.

- The IndustrialControlSystems package is free

software; it can be redistributed and/or modified under the terms

of the Modelica license, see the license conditions and the

accompanying disclaimer in the documentation of package

Modelica in file "Modelica/package.mo".

Generated at 2026-04-15T18:18:36Z by OpenModelicaOpenModelica 1.26.3 using

GenerateDoc.mos