This model demonstrates the correct

behaviour of a transformer with a tap-changer logic of type

INTERVAL.

The test circuit is composed by

a transformer whth a simple linear load. The transformer is

supplied by an ideal infinte bus with variable

voltage.

The linear load is obtained

using a real bus with fixed voltage, the internal impedance of the

bus is used as linear load.

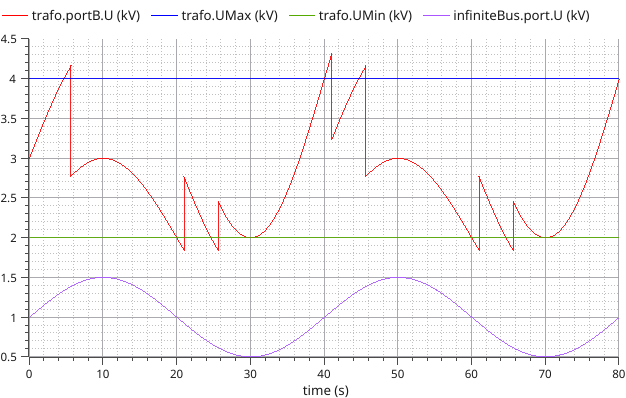

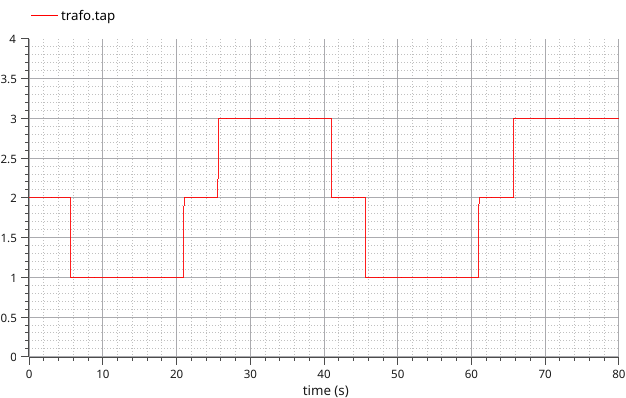

The voltage applied at the

transformer primary input has a sinusoidal shape, the tap-changer

logic follows the shape of said voltage. The tap position decreases when the monitored

voltage portB.U becomes higher than UMax threshold, and increases

when said monitored voltage becomes lower than UMin

threshold.

Values of voltages and and

transformer ratio for each tap position are not realistic, they are

just to show the tap changer logic behaviour.

Generated at 2026-04-15T18:18:36Z by OpenModelicaOpenModelica 1.26.3 using

GenerateDoc.mos